标签

日期

Place

创建时间

Jan 8, 2026 01:53 PM

前置知识

CPU的设计步骤

- 拟定指令系统

- 格式、寻址方式、指令类型

- 确定总体结构

- 寄存器、ALU、数据通路

- 安排时序

- 设置时序信号

- 拟定指令流程和微命令序列

- 画流程图(寄存器传送级)、列微操作时间表

- 形成控制逻辑

用到的相关思想和结论

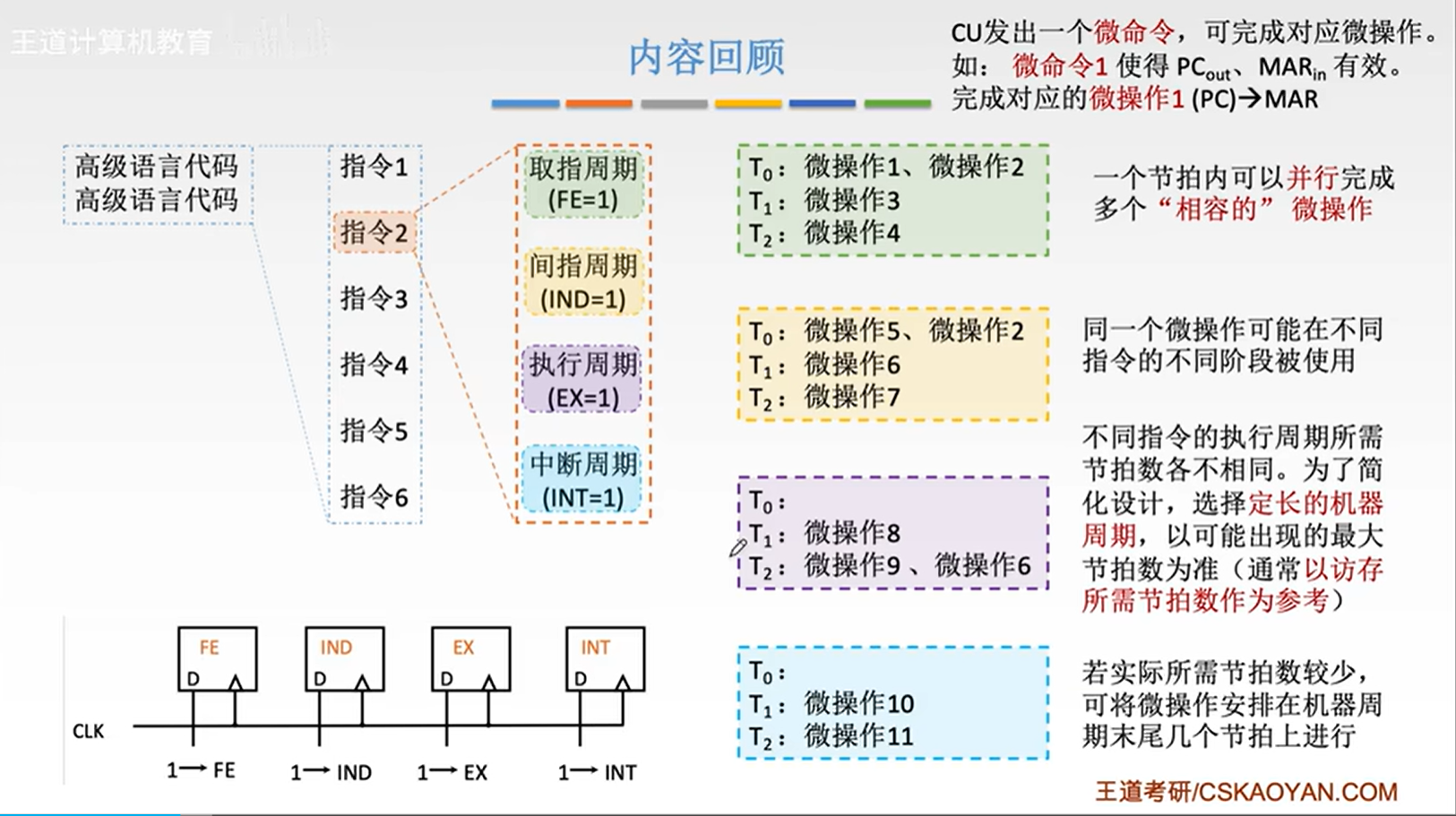

根据指令操作码、目前的机器周期、节拍信号、机器状态条件,即可确定现在这个节拍应该发出哪些微命令

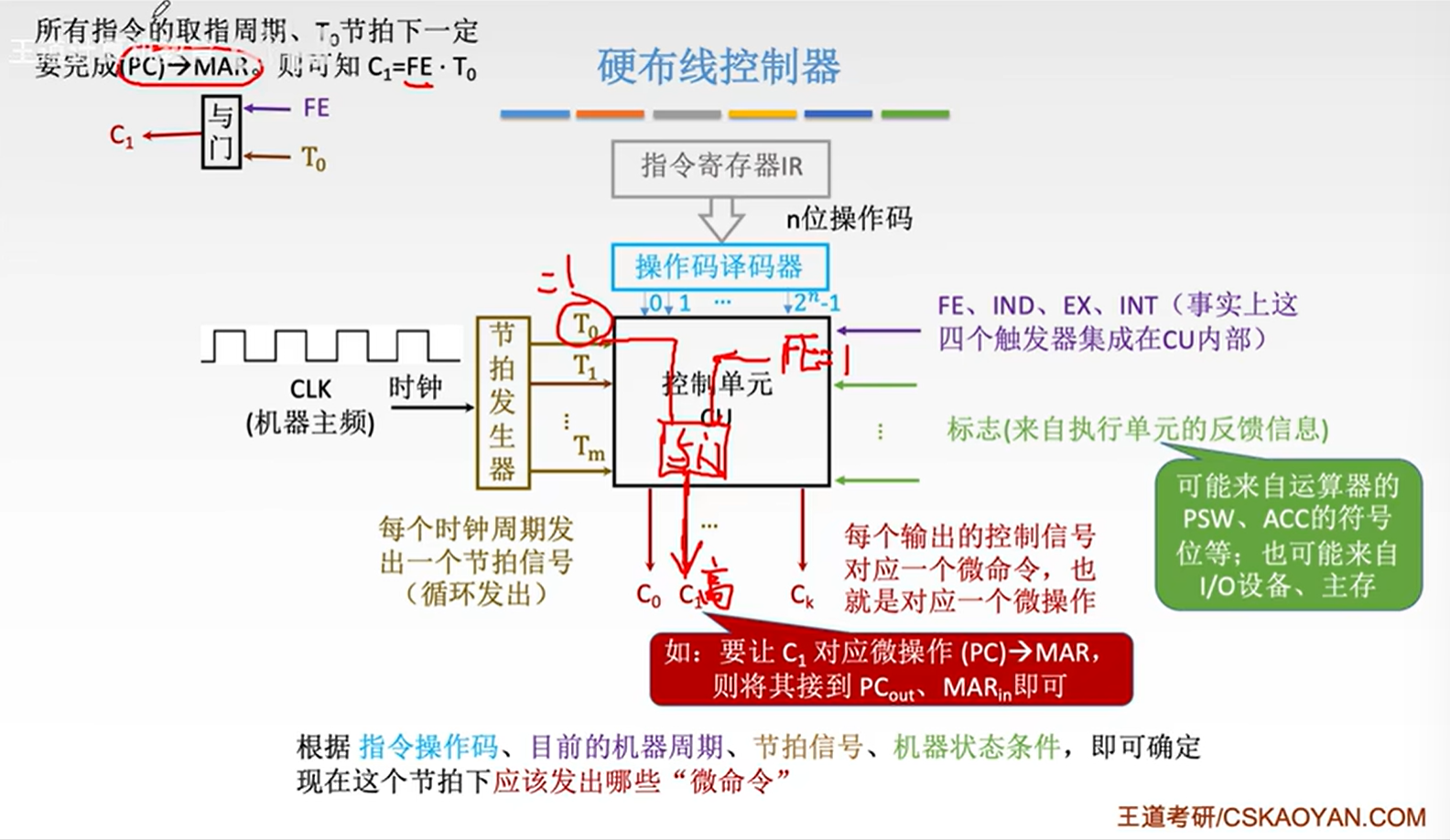

组合逻辑设计

组合逻辑控制单元框图

根据==指令操作码==、==目前的机器周期==、==节拍信号==、机器状态条件,即可确定现在这个节拍应该发出哪些微命令

- 指令操作码:

- 指令的操作码是决定控制单元发出不同控制信号的关键

- 将存放在IR的n维操作码经过一个译码电路产生2^n个输出,每对应一种操作码便有一个输出送至CU

- 目前的机器周期: FE IND EX INT这四个触发器判断目前处于的机器周期状态(这四个触发器集成在CU内部)

- 节拍信号: 根据节拍发生器的输出,依次让不同的节拍输出高电平

控制单元的时钟输入实际上是一个脉冲序列,其频率等于机器主频,它使CU能按一定的节拍发出各种控制信号,以时钟为计数脉冲,通过一个计数器(节拍发生器),便可产生一个与时钟周期等宽的节拍序列

- 机器状态条件 标志---来自于执行单元的反馈信息

- 总结

组合逻辑设计步骤

- 引入

- 整体流程

- 分析每个阶段的微操作序列(取指、间址、执行、中断)

- 确定哪些指令在什么阶段、在什么条件下会用到的微操作

- 选择CPU的控制方式

- 定长机器周期/不定长机器周期

- 每个机器周期安排几个节拍

- 安排微操作时序

- 如何用上述确定的节拍内完成整个周期内所有的微操作

- 电路设计

- 确定每个微操作命令对应的逻辑表达式,并用电路实现

- 列出操作时间表

- 写出微操作命令的最简表达式

- 画出逻辑图

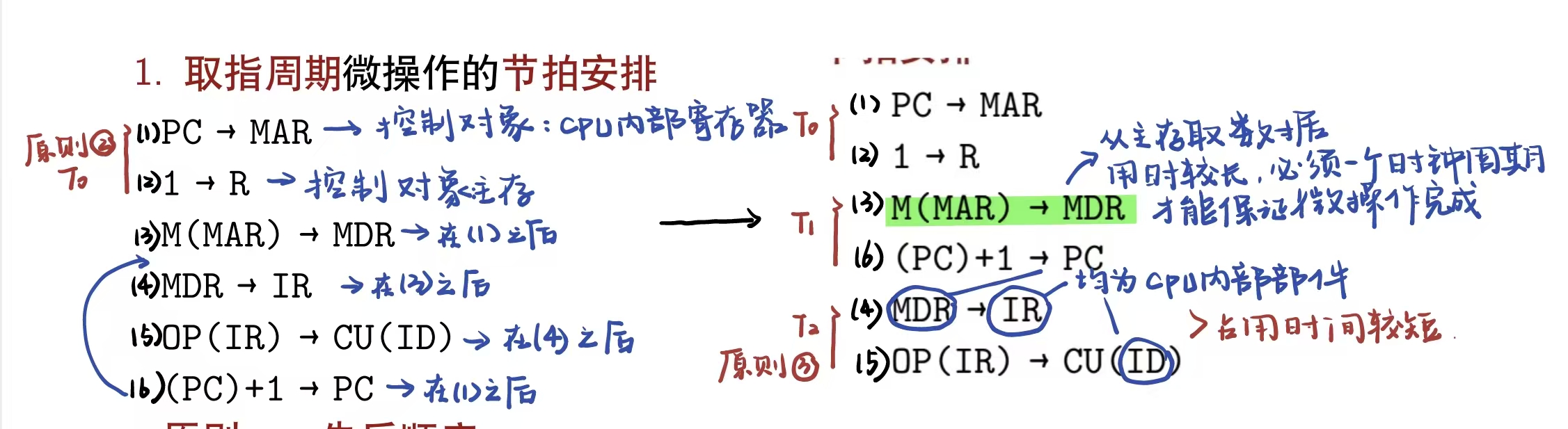

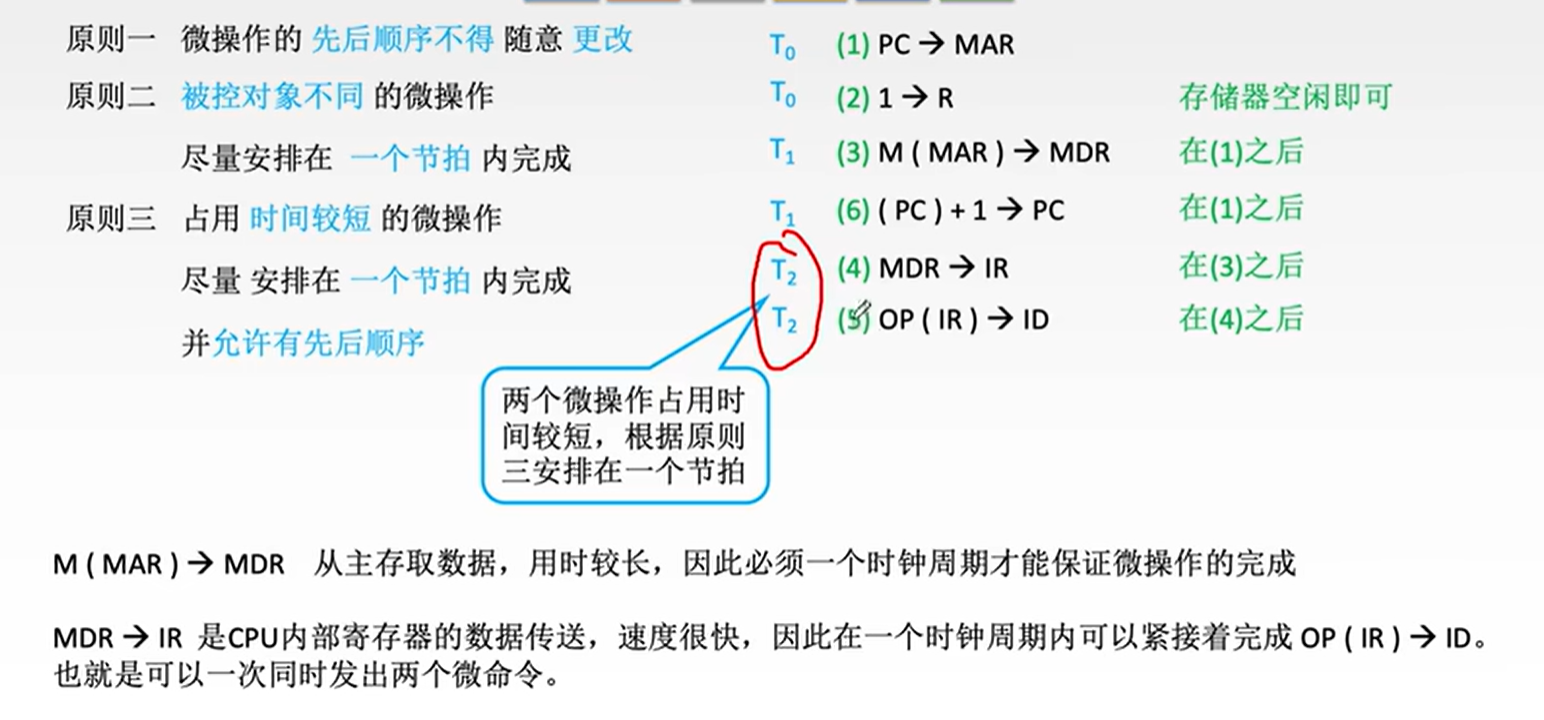

- 详细说明 假设机器采用同步控制,每个机器周期包含3个节拍 (1)分析每个阶段的微操作序列 (2)选择CPU的控制方式 假设机器采用同步控制,每个机器周期包含3个节拍 (3)安排微操作时序🔆 安排微操作时序的原则/注意点:

- 有些微操作的次序是不容改变的,安排微操作节拍时必须注意微操作的先后顺序

- 凡是被控对象不同的微操作(硬件资源不冲突),若能在一个节拍内执行,应尽可能安排在同一个节拍内,以节省时间

- 如果有些微操作所占的时间不长,应该将他们安排在一个节拍内完成,并且允许这些微操作有先后顺序(短时可挤)

取指周期:

间址周期:

T0 Ad(IR) → MAR

1 → R

T1 M(MAR) → MDR

T2 MDR → Ad(IR)

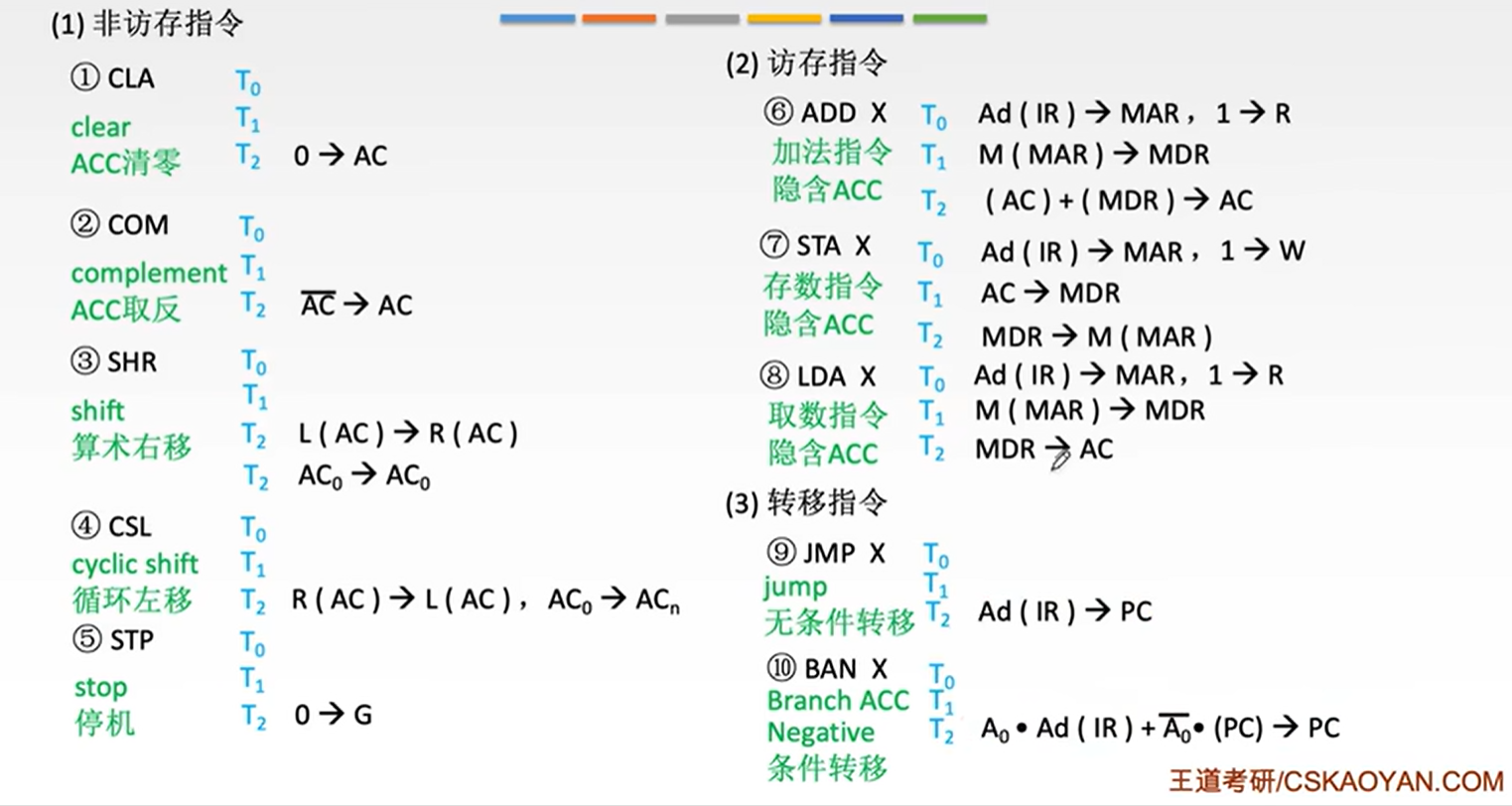

执行周期:

若实际所需的节拍数较少,可将

微操作安排在机器周期末尾几个节拍进行

中断周期:

假设程序断点存入主存0号地址单元

T0 0 → MAR, 1 → W

T1 PC → MDR

T2 MDR → M(MAR), 向量地址 → PC

假设程序断点存入堆栈

T0 (SP)-1 → MAR, 1 → W

T1 PC → MDR

T2 MDR → M(MAR), 向量地址 → PC

(4)电路设计

- 列出操作时间表

- 列出在取指、间址、执行、中断周期,T0、T1、T2节拍内有可能用到的所有微操作

- 写出微操作命令的最简表达式

- 画出逻辑图

特点

- 思路清晰、简单明了

- 每一个微操作命令都对应一个逻辑电路,这种控制单元的线路结构十分庞杂,不规范

- 指令系统功能越全,微操作命令越多,线路越复杂,调试困难,修改困难

- 使用纯硬件实现控制,速度快

- 一般用于RISC

补充题型

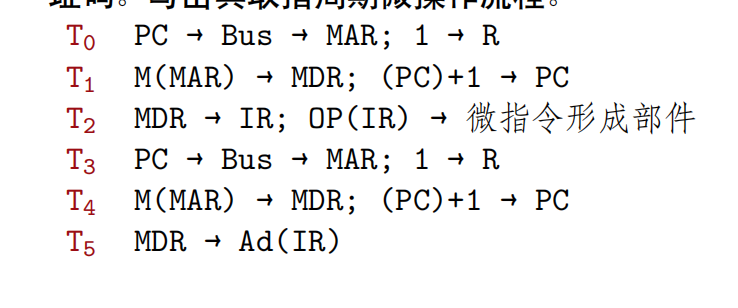

指令字长=n倍存储字长

若指令ADD Addr(ACC寄存器内容加上以Addr为地址的内存单元内容,结果存在ACC寄存器中)为两字指令,第一个字中包含操作码,第二个字中包含地址码

(采用大端序,高8位操作码,低8位地址码)

写出取指周期微操作流程

【很像间接寻址,只是多了PC+1->PC,是为了取得形式地址】

取形式地址--->取实际地址--->取数