标签

04存储器

日期

Place

创建时间

Jan 8, 2026 01:47 PM

存储器概述

定义

- 存储器是记忆信息的实体,是数字计算机具备存储数据和信息能力,能够自动连续执行程序,进行广泛的信息处理的重要基础

- 存储器是计算机系统中的记忆设备,用来存放程序和数据

分类

(1)按存储介质分类

存储介质是指能寄存‘0’、‘1’两种代码并能区别两种状态的物质或元器件

易失:

- 半导体存储器---存储元件由半导体器件组成的存储器

- 现代半导体存储器都用超大规模集成电路工艺制成芯片

- 优点:体积小、功率低、存取时间短

- 缺点:当电源消失,所存信息也随即丢失,是一种易失性存储器

- 按材料的不同

- 双极型(Transistor-Transistor-Logic,TTL)

- 高速

- 金属氧化物(Metal-Oxide-Semiconductor,MOS)

- 高集成度+制造简单+成本低廉+功耗小 不易失:

- 磁表面存储器

- 磁表面存储器是在金属或塑料基体的表面上涂一层磁性材料作为记录介质,工作时磁层随载磁体高速运转,用磁头在磁层上进行读 / 写操作,故称为磁表面存储器

- 非易失性

- 磁芯存储器

- 磁芯是由硬磁材料做成的环状元件,在磁芯中穿有驱动线(通电流)和读出线,这样便可进行读 / 写操作

- 目前几乎不被采用

- 不易失的永久记忆存储器

- 光盘存储器

- 光盘存储器是应用激光在记录介质(磁光材料)上进行读 / 写的存储器,具有非易失性的特点

- 记录密度高、耐用性好、可靠性高、可乎互换性强

(2)按存取方式分类

- 存取时间与物理地址无关(随机访问)

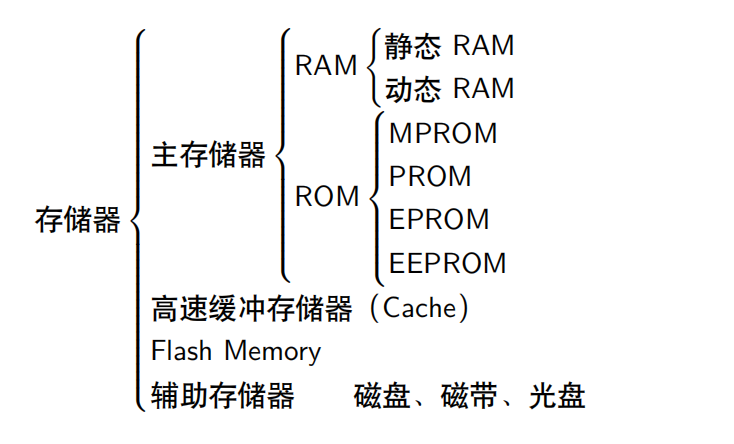

- 随机存储器(RAM)

- RAM是一种在程序执行过程中可读/可写的存储器

- 存储器的任何一个存储单元的内容都可以随机存取,且存储时间与存储单元的物理位置无关

- 计算机系统中的主存采用此种存储器

- 按照存储信息原理不同可进行分类:

- 静态RAM(以触发器原理寄存信息)

- 动态RAM(以电容充放电原理寄存信息)

- 只读存储器(ROM)

- 能对其存储的内容读出,而不能重新写入的存储器,这种存储器一旦存入了原始信息后,在程序执行过程中,只能将内部信息读出,而不能随意重新写入新的信息去改变原始信息

- 通常存放固定不变的程序、常数和汉字字库

- 与随机存储器可共同作为主存的一部分,统一构成主存的地址域

- 存取时间与物理地址有关(串行访问)---如果对存储单元进行读、写操作时,需要按其物理位置的先后顺序寻找地址,则这种存储器称为串行访问存储器

- 顺序存取存储器

- 不论信息处在哪个位置,读 / 写时必须从其介质的始端开始按顺序寻找

- 典型:磁带

- 直接存取存储器

- 在对磁盘读 / 写时,首先直接指出该存储器中的某个小区域(磁道),然后再顺序寻访,直至找到位置。故其前段是直接访问,后段是串行访问

- 典型:磁盘 (3)按在计算机中作用分类

存储器的层次结构

理解两个+一个重要的图像:

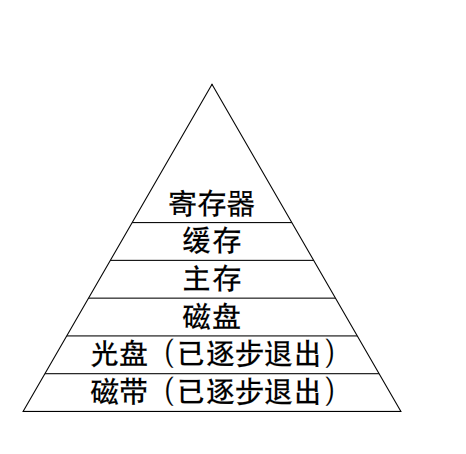

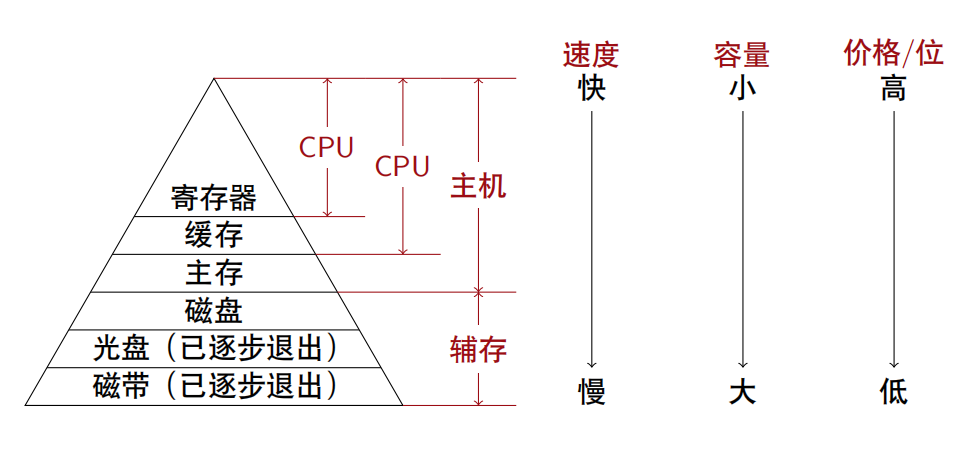

- 存储器速度、容量和位价的关系 对上图的理解: 存储器有三个主要的性能指标:

- 速度

- 容量

- 位价 图中由上至下,位价越来越低,速度越来越慢,容量越来越大,CPU访问的频度也越来越少(离CPU越来越远)

寄存器---通常制作在CPU芯片内。寄存器中的数直接在CPU内部参与运算

缓存---主存速度与CPU速度差距较大,为了使他们之间的速度更好地匹配,在主存与CPU之间插入一种比主存速度更快、容量更小的高速缓冲存储器Cathe

主存---存放将要参与运行的程序和数据

summary:

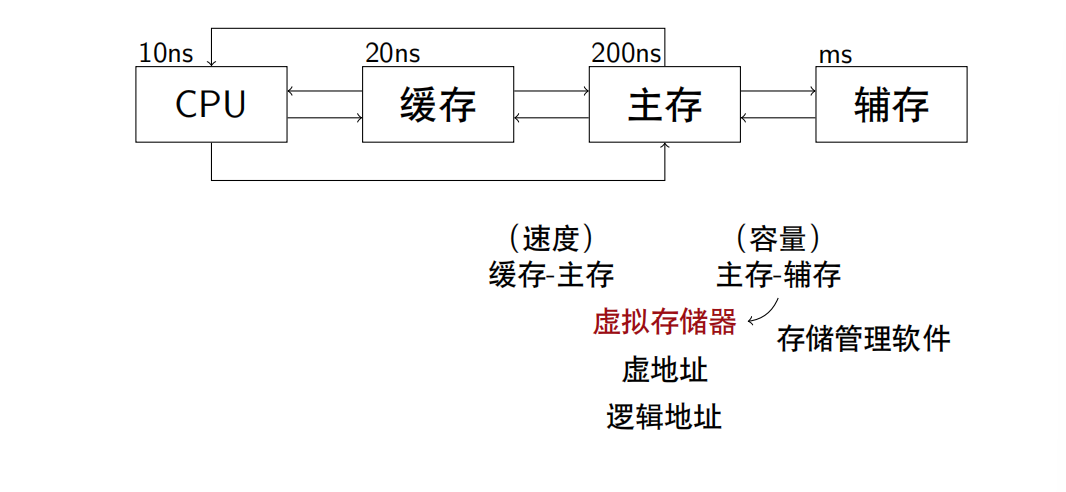

- 缓存-主存层次+主存-辅存层次 缓存-主存层次:解决CPU和主存速度不匹配的问题

由于缓存的速度比主存的速度高,只要将 CPU 近期要用的信息调入缓存,CPU 便可以直接从缓存中获取信息,从而提高访存速度。但由于缓存的容量小,因此需不断地将主存的内容调入缓存,使缓存中原来的信息被替换掉。

主存-辅存层次:解决存储系统的容量问题

辅存的速度比主存的速度低,而且不能和 CPU 直接交换信息,但它的容量比主存大得多,可以存放大量暂时未用到的信息。当 CPU 需要用到这些信息时,再将辅存的内容调入主存,供 CPU 直接访问。

主存与 Cache 之间的数据调度是由硬件自动完成的,对程序员是_透明_的。而主存—辅存之间的数据调度,是由硬件和操作系统(采用虚拟存储技术)共同完成的

补充:在主存-辅存这一层次的不断发展中,逐渐形成了虚拟存储系统

- 虚地址/逻辑地址:程序员编程时使用的地址,是虚拟存储器的地址空间

- 实地址/物理地址:程序执行时真正访问的主存实际地址,是实实在在的主存单元地址

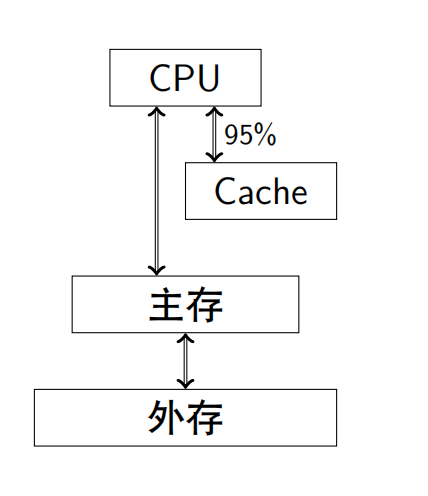

- 多级存储体系 CPU(中央处理器):是计算机的核心运算部件,需要频繁访问存储器获取指令和数据 Cache(高速缓存):是速度极快但容量较小的存储器。图中 “95%” 表示 CPU 大约 95% 的访存需求可以直接通过 Cache 满足主存(主存储器):是 CPU 可以直接访问的存储器,容量比 Cache 大,但速度比 Cache 慢。当 Cache 中没有所需信息时,CPU 会访问主存。同时,主存与外存之间进行数据交换,用于补充主存的容量不足