type

status

date

slug

summary

tags

category

icon

password

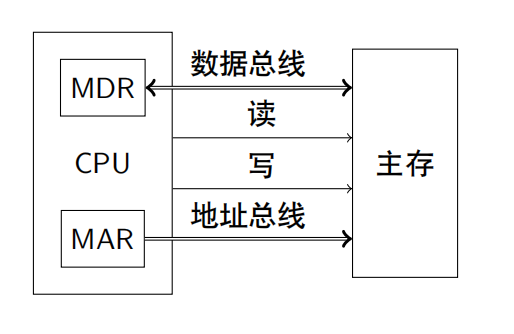

主存的基本组成

- MAR(存储器地址寄存器):接收来自地址总线的地址信息,用于确定要访问的存储单元位置。

- 译码器:对 MAR 中的地址进行译码,将其转换为存储体中具体存储单元的选择信号。

- 驱动器:放大译码后的信号,驱动存储体中对应的存储单元,使其处于可访问状态。

- 存储体:是存储器的核心,由大量存储单元组成,用于存放指令和数据。

- 读写电路:在控制电路的 “读” 或 “写” 命令控制下,完成对存储体中数据的读取或写入操作。

- MDR(存储器数据寄存器):是数据的暂存部件,读取时暂存从存储体中读出的数据,写入时暂存要写入存储体的数据;同时通过数据总线与 CPU 或其他部件进行数据交换。

- 控制电路:接收 “读”“写” 控制信号,协调上述各部件的工作,保证读写操作的有序进行。

图中译码器、驱动器、读写电路均制作在存储芯片中

MAR、MDR制作在CPU芯片内

存储芯片和CPU芯片可通过总线连接

主存和CPU的联系

- 当要从存储器中读出某一信息字时,首先由CPU将该字的地址送至MAR,经地址总线送至主存,然后发出读命令。主存接到读的命令后,得知需将该地址单元的内容读出,便完成读操作,将该单元的内容读至数据总线上

- 若要向主存存入一个信息字时,首先CPU将该字所在主存单元的地址经MAR送到地址总线,并将信息字送入MDR,然后向主存发出命令,主存接到命令后,便将数据线上的信息写入对应地址线指出的主存单元中

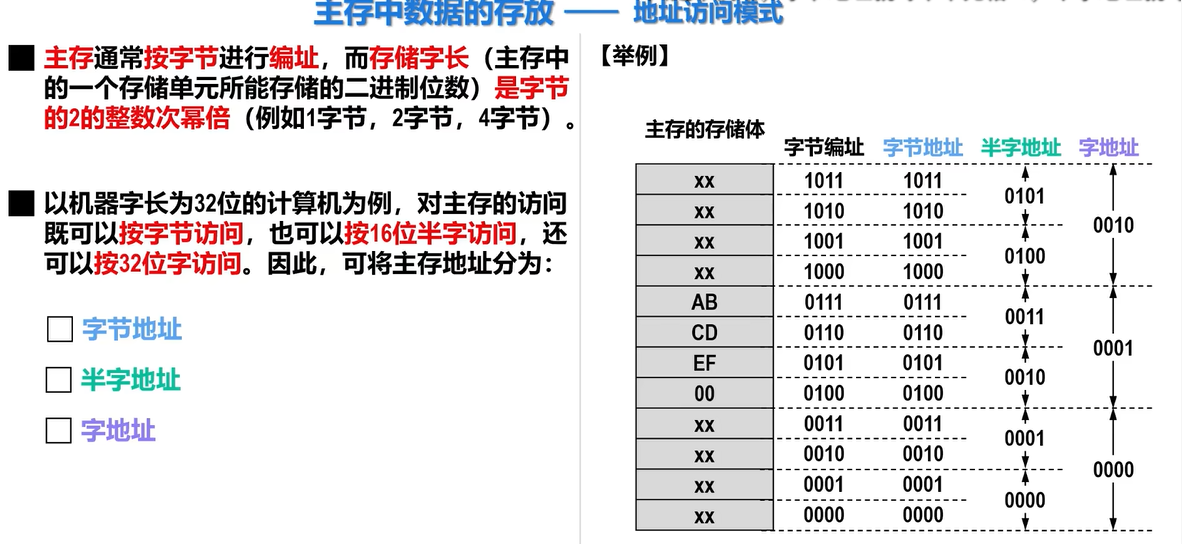

🔆主存中存储单元地址的分配

补充知识

机器字长:CPU一次能够处理的二进制数据位数

存储字长:主存中一个存储单元所能存储的二进制位数

机器字长与存储字长不一定相同

- 主存通常按字节进行编址,而存储地址时字节的2的整数次幂倍

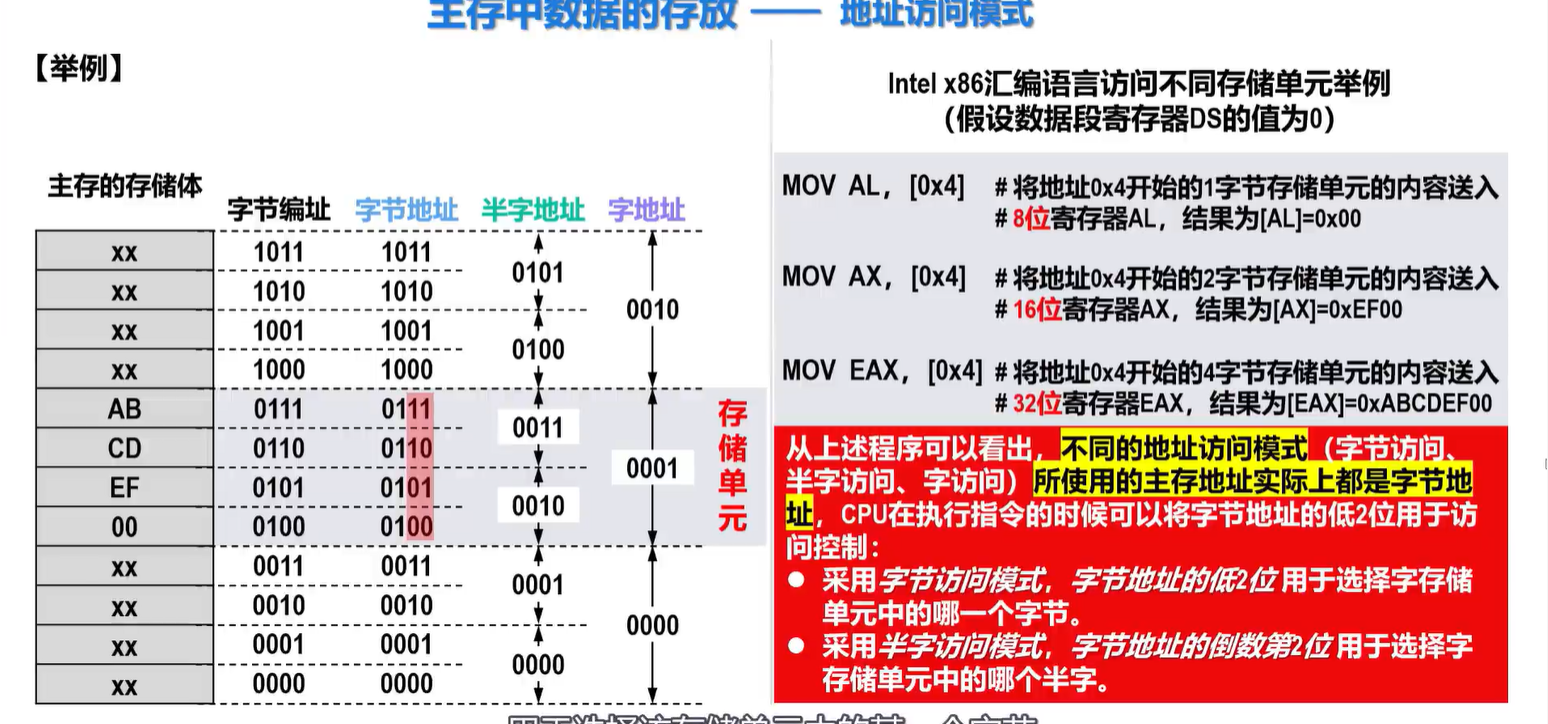

- 以机器字长为32位的计算机为例,对主存的访问既可以按字节访问,也可按16位半字访问,还可按32位字访问

- 字节地址---主存按字节编址的字节地址

- 半字地址

- 字地址

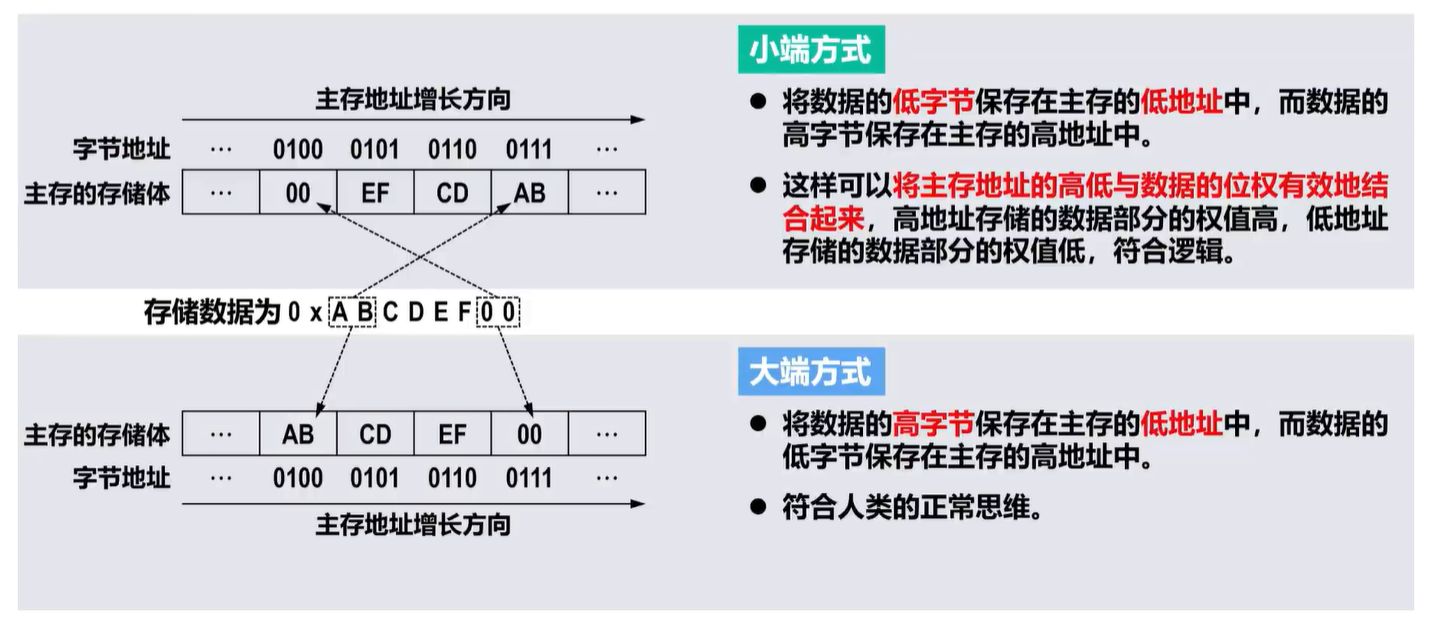

小端法 vs 大端法

大端法:高位字节排放在内存的低地址端

小端法:低位字节排放在内存的低地址端

主存的技术指标

- 存储容量

- 主存能存放二进制代码的总位数

- 存储容量=存储单元个数x存储字长=存储单元个数x存储字长/8

- 存储速度

- 存取时间/存储器的访问时间

- 启动一次存储器操作开始到完成该操作所需的全部时间(从本次读/写开始至本次读/写结束)

- 读出时间:从存储器接收到有效地址开始,到产生有效输出所需的全部时间

- 写入时间:从存储器接收到有效地址开始,到数据写入被选中单元为止所需的全部时间

- 存取周期

- 存储器进行连续两次独立的存储器操作所需的最小间隔时间

- 存储器的带宽

- 单位时间内存存取的信息量(存取信息量/时间)

- Author:luckylotus

- URL:http://preview.tangly1024.com/article/29f0a43b-63ed-81df-bd68-c675cac87907

- Copyright:All articles in this blog, except for special statements, adopt BY-NC-SA agreement. Please indicate the source!